#### DIPLOMARBEIT

# Memory Allocation Strategies for Large Volumetric Data-Sets

ausgeführt am

Institut für Computergrafik und Algorithmen der Technischen Universität Wien

unter Anleitung von

Ao. Univ. Prof. Dipl.-Ing. Dr. techn. Eduard Gröller Dipl.-Inform. Sören Grimm

$\operatorname{durch}$

Michael Knapp Allhangstrasse 26 3001 Mauerbach

| 7. Dezember 2004 |              |

|------------------|--------------|

| Datum            | Unterschrift |

## Michael Knapp

# Memory Allocation Strategies for Large Volumetric Data-Sets

Diploma Thesis

supervised by

Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Eduard Gröller Dipl.-Inform. Sören Grimm

Institute of Computer Graphics and Algorithms

Vienna University of Technology

## Abstract

Since the development of medical three dimensional imaging devices in the 1970s, volumetric data processing has tremendously gained in importance. With the growing size of the data-sets, exhausting the capabilities of the hardware of its time, methods for efficient volumetric data processing have been always a hot topic. In this diploma thesis two approaches for processing large volumetric data-sets are presented. Both approaches utilize a block volume for storing the data. Further data compression and out-of-core processing are incorporated. Efficiency is achieved by processing only the required portion of data while omitting the non-related data having no effect on the intended result of the algorithm. This is supported by utilization of the knowledge about access patterns of the algorithms. Also methods for optimizing the efficiency by exploiting architectural properties of the computer hardware are presented.

# Kurzfassung

Seit der Einführung von medizinischen dreidimensionalen bildgebenden Verfahren in den 1970er Jahren gewann die Verarbeitung von volumetrischen Daten massiv an Bedeutung. Mit der wachsenden Größe der Daten, die die Kapazitäten der Hardware ihrer Zeit laufend auslastete, waren Methoden für die effiziente Verarbeitung von volumetrischen Daten immer wichtig. In dieser Diplomarbeit werden zwei Methoden für die Verarbeitung großer volumetrischer Daten vergestellt. Beide Methoden verwenden eine geblockte Datenstruktur für die Verwaltung der Daten. Weiters werden Datenkompression und Out-of-Core-Methoden integriert. Effizenz wird durch das Verarbeiten von ausschließlich für das Ergebnis eines Algorithmus relevanten Daten erreicht, wobei nicht relevante Daten, die keinen Effekt aus das zu erzielende Ergbenis haben, von vornherein ausgeschlossen werden. Die Effizienz dieser Methoden wird unter Beachtung der Zugriffsmuster von Algorithmen verbessert. Weiters werden Methoden zur weiteren Effizienzsteigerung vorgestellt, die die architekturiellen Eigenheiten der Computer Hardware ausnützen.

# Contents

| 1 | Inti | roduction                                                | 1  |

|---|------|----------------------------------------------------------|----|

| 2 | Sta  | te of the Art                                            | 4  |

|   | 2.1  | Introduction                                             | 4  |

|   | 2.2  | General Volumetric Data Handling Approaches              | 4  |

|   |      | 2.2.1 Virtual Memory                                     | 4  |

|   |      | 2.2.2 Application Controlled Paging Mechanism            | 5  |

|   | 2.3  | Specific Volumetric Data Handling Approaches             | 5  |

|   |      | 2.3.1 Iso-Surface Extraction Methods                     | 5  |

|   |      | 2.3.2 Volume Rendering                                   | 6  |

|   | 2.4  | Data Reduction by Wavelet-Transformation and Compression | 8  |

| 3 | Cor  | mputer System Issues                                     | 9  |

|   | 3.1  | Introduction                                             | 9  |

|   | 3.2  | Data Processing Components                               | 10 |

|   | 3.3  |                                                          | 11 |

|   |      |                                                          | 11 |

|   |      |                                                          | 14 |

|   |      |                                                          | 17 |

|   |      |                                                          | 20 |

|   | 3.4  | _                                                        | 23 |

| 4 | Blo  | ck Volume Memory Layout                                  | 24 |

|   | 4.1  | Volumetric Data Properties                               | 24 |

|   |      | 4.1.1 Non-Relevant Data                                  | 25 |

| CONTENTS | iii |  |

|----------|-----|--|

|          |     |  |

|   |     | 4.1.2  | Memory Access                          | 26 |

|---|-----|--------|----------------------------------------|----|

|   |     | 4.1.3  | Out-of-Core Processing                 | 28 |

|   |     | 4.1.4  | Application Examples                   | 29 |

|   | 4.2 | Block  | Volume                                 | 30 |

|   |     | 4.2.1  | Sequential Volume                      | 30 |

|   |     | 4.2.2  | Motivation of the Block Volume         | 31 |

|   |     | 4.2.3  | Contiguous Block Volume                | 33 |

|   |     | 4.2.4  | Fragmented Block Volume                | 41 |

|   |     | 4.2.5  | Shared Block Volume                    | 43 |

|   |     | 4.2.6  | Compressed Shared Block Volume         | 47 |

|   | 4.3 | Volum  | ne Processing Hierarchy                | 50 |

| 5 | Me  | mory A | Allocation Strategies                  | 53 |

|   | 5.1 | Introd | uction                                 | 53 |

|   | 5.2 | Strate | gy 1: Dynamic Block Allocation         | 54 |

|   |     | 5.2.1  | Components                             | 54 |

|   |     | 5.2.2  | Internal Operating Sequence            | 55 |

|   |     | 5.2.3  | Conclusion                             | 58 |

|   | 5.3 | Strate | gy 2: Block Mapping                    | 59 |

|   |     | 5.3.1  | Addressing the Sub-Volumes             | 60 |

|   |     | 5.3.2  | Components                             | 62 |

|   |     | 5.3.3  | Out-of-core Volumetric Data Processing | 62 |

|   |     | 5.3.4  | Operation of the Mapped Block Volume   | 63 |

|   |     | 5.3.5  | Conclusion                             | 64 |

| 6 | Imp | olemen | tation                                 | 65 |

|   | 6.1 | Introd | uction                                 | 65 |

|   | 6.2 | Dynar  | nic Block Allocation                   | 65 |

|   | 6.3 | Mappe  | ed Block Volume                        | 67 |

| 7 | Res | ults   |                                        | 70 |

|   | 7.1 | Gener  | al Remarks                             | 70 |

|   |     | 7.1.1  | Data Access                            | 70 |

|   |     | 7.1.2  | Decompression Speed                    |    |

|   |     |        |                                        |    |

| CONTENTS | iv |

|----------|----|

|----------|----|

|   | 7.2 | Block Volume Results                        |

|---|-----|---------------------------------------------|

|   | 7.3 | Ray-Casting on the Block Volume             |

|   |     | 7.3.1 Dynamic Block Allocation              |

|   |     | 7.3.2 Mapped Block Volume                   |

| 8 | Sun | nmary 84                                    |

|   | 8.1 | Introduction                                |

|   |     | 8.1.1 Data Processing Issues                |

|   | 8.2 | Sequential Layout                           |

|   | 8.3 | Contiguous Block Volume                     |

|   |     | 8.3.1 Absolute Addressing                   |

|   |     | 8.3.2 Relative Addressing Scheme            |

|   | 8.4 | Fragmented Block Volume                     |

|   | 8.5 | Shared Block Volume                         |

|   |     | 8.5.1 Border Issue                          |

|   | 8.6 | Compression and Out-of-core                 |

|   | 8.7 | Dynamic Block Allocation                    |

|   |     | 8.7.1 Operation                             |

|   |     | 8.7.2 Discussion                            |

|   | 8.8 | Mapped Block Volume                         |

|   |     | 8.8.1 Operation of the Mapped Block Volume  |

|   |     | 8.8.2 Discussion of the Mapped Block Volume |

|   | 8.9 | Conclusion                                  |

|   | 0.0 |                                             |

# Chapter 1

# Introduction

Since the introduction of the computer tomography scanner by G.N. Hounsfield in the early 1970s processing of volumetric data tremendously gained in importance. Computer tomography is the reconstruction of cross-sectional images from multiple one dimensional scans along lines from different angles on a plane. The reconstruction of a series of such cross-sectional dimensional images results in a three dimensional, i.e. volumetric, data-set. The essential steps contributing to the computer tomography technology as it is used today had happened already in the decades before.

In 1895, the so-called X-rays were discovered by W.C. Röntgen. The X-rays, high energetic electro-magnetic radiation with wave-lengths in the picometer range, are able to permeate compact structures without being dispersed too much. Depending on the material of the structures, the X-rays are absorbed in varying intensity.

In the 1960s A.M. Cormack, physicist at the Groote Schuur Hospital in Cape Town / South Africa, developed a mathematical model for the absorption distribution of X-rays in the human body.

A mathematical model of the reconstruction of cross-sectional images from one dimensional transmission measurements was introduced by J.H. Radon in 1917.

In the early 1970s, these three relevant contributions have been incorporated and realized in hardware by G.N. Hounsfield. In 1972 the first clinical diag-

nostics based on computer tomography images were made. A few years later several thousand computer tomography scanners were in use worldwide. The first scanners had a slice size of 80x80 pixel and a thickness of 13 millimeter. Slice is a synonym for the reconstructed cross-sectional image. For example scanning the human head would result in approximately 150 slices.

In the early days of computer tomography, it was sufficient to examine a single slice, in order to conduct a medical diagnosis. At this time, scanning a single slice took 300 seconds. Later, with the reduction of the scanning time down to a few seconds, the acquisition of a series of slices at once became common. It was sufficient to examine the scanned data slice by slice like ordinary x-ray images.

With the up-come of personal workstations in the 1980s, digital processing of the computer tomography data became more and more popular. Over the years, the computer tomography technology improved: 1990 the spiral computer tomography was introduced and the scanner resolution increased. Now, the slice resolution of modern scanners is at 1024x1024 with a slice thickness of 0.5 millimeter. A scan usually results in a series of several hundred slices.

This is the point, where volumetric data processing becomes indispensable: Examining hundreds of slices one by one is not feasible anymore. The introduction of an additional processing step between the data acquisition and the visualization for diagnostic purpose is necessary. This processing step is referred to as *volumetric data processing*.

The past years have shown, that the size of the volumetric data-sets has increased as fast as the CPU processing power and memory size. During this time period the data density, i.e. the portion of data acquired for the same volume, increased by 100, while the CPU processing power increased by a factor of 1000, the memory bandwidth increased by a factor of 500 and the mass storage interface bandwidth increased by a factor of 40. Thus efficient data handling is an important issue of volumetric data processing. Today the common silicon technology reached its physical limits, whereas in the computer tomography area there is still much potential for further increase of the data quantity: the recent introduction of 16-slice scanners, better de-

tectors and the emergence of multi-modal data let expect a further increase of the amount of data to be processed.

Common computer architecture is sufficient for average applications, however its complex architecture cannot optimally serve applications with exceptional resource requirements. Such exceptional requirements are needed in the field of volumetric data processing, where very efficient data transfer capabilities in all components, i.e. CPU, memory and mass storage devices, are required. The memory requirements for this type of applications regularly tend to exceed the available memory resources, so that the data often must be processed directly from mass storage devices, which are very slow compared to the memory or caches.

For optimally utilizing the data transfer capabilities of these components, the development of specific algorithms exploiting the architectural advantages of the common computer hardware is necessary.

# Chapter 2

## State of the Art

#### 2.1 Introduction

The main focus of this diploma thesis is to present a generic approach to out-of-core volume processing. A data processing approach is referred to as *out-of-core*, if the data cannot completely be held in the available physical memory. Most approaches assume that the data is completely memory-resident and directly accessible without any data initializing processes beforehand. There are several publications which present out-of-core approaches for specific volumetric data processing applications, for example, direct volume rendering or surface extraction algorithms.

# 2.2 General Volumetric Data Handling Approaches

## 2.2.1 Virtual Memory

A generic out-of-core approach, which is widely used by current operating systems is the concept of *virtual memory*. *virtual memory* is a common approach for providing a significantly larger memory space than physical memory is available. This is achieved by utilizing the paging mechanism of the CPU and the operating system.

The virtual memory is split into pages, memory areas of the common size of 4 kilobytes. In physical memory only the currently processed pages are kept the others are stored on the hard-disk. The paging mechanism of the CPU and additional processes in operating system load on store the pages on the hard-disk when required. This mechanism is completely invisible to the applications, so no special code for using virtual memory is required. The virtual memory is more or less a generic out-of-core processing approach. It is sufficient for common applications on common computer systems, but its efficiency dramatically degrades when processing large amounts of data. This is due to the relatively small pages an high latency of the paging mechanism. Therefore, for large data processing more efficient approaches are required.

## 2.2.2 Application Controlled Paging Mechanism

There are only very few approaches for general volumetric data handling. For example, Cox et al. [5] describe such an approach: It is stated that a complete reliance on operating system virtual memory for out-of-core visualization leads to poor performance due to the complexity of the paging mechanism of the CPU and operating system as stated in the previous section. To overcome this issue they developed a paged segment system, where application control over several principles of memory management can significantly improve the performance. This is achieved by sparse traversal, i.e. loading only required data, usage of a blocked data storage layout and controlling the page size.

# 2.3 Specific Volumetric Data Handling Approaches

#### 2.3.1 Iso-Surface Extraction Methods

Many approaches for iso-surface extraction algorithms have been developed. Some of them also support out-of-core. For surface extraction methods, auxiliary structures like tree-based search-structures are employed for sparse traversal, i.e. processing of only required data while excluding non-relevant

data. For example, the interval tree is an efficient search structure to retrieve intervals (i.e. minimum and maximum data value of a 2x2x2 cube) containing a given query data value. Cignoni et al. [4] employ interval trees for fast location of relevant cells, i.e. a cube of 8 adjacent voxels intersected by an iso-surface. Further issues about storage requirements and other operations affecting the iso-surface extraction are addressed.

It has been shown that the search space can be considerably reduced through tree-based search-structures. They are very efficient for relatively small datasets, which fit easily into the memory of common computer systems. However, due to their additional memory requirements, their application for large data-sets is difficult. Saupe et al. [14] states, that such search-structures can use up more memory than the original data itself. An approach trading off memory usage for extraction speed is presented: A hybrid algorithm combining binary space partition (BSP) trees with fast search methods at leaf nodes of the BSP tree and memory-free linear search at the remaining leaf nodes.

Chiang et al. [3] extend the interval tree for out-of-core iso-surface extraction: A novel application for the extraction of iso-surfaces from volumetric data employing an I/O-optimal interval tree is presented. A search structure is generated from the data-set in a preprocessing step and stored on disk beside the volumetric data. The extraction algorithm efficiently processes the data directly from disk and has very low memory requirements leaving most of the memory for storing the iso-surface.

### 2.3.2 Volume Rendering

Yang et al. [17] have developed a data-driven execution model for ray-casting that achieves a maximum overlap between rendering computation and disk I/O. Modern hard-disk controllers are able to autonomously transfer data to and from the memory without utilizing CPU resources. During the transfer, the CPU can be used for data processing. Further an application-specific file system maximizing the overlap between disk I/O and computation is introduced.

Bajaj et al. [1] propose a parallel/distributed ray-casting scheme for very large volume data. This method, based on data compression, attempts to enhance the rendering speedups by quickly reconstructing voxel data from local memory rather than expensively fetching them from remote memory spaces. This scheme minimizes the communication between the distributed processing elements during rendering computation.

Guthe et al. [7] present an interactive exploration method for animated volumetric data. The method employs video encoding methods, i.e. wavelet transformation, motion compensation, quantization and various encoding schemes for the resulting wavelet coefficients, which is optimized for good visual impression of the reconstructed volume. Further the temporal coherency is exploited. It was possible to achieve interactive frame rates for images with a resolution of 256x256 pixel.

In another work Guthe et al. [8] present an approach to interactive rendering of large volume data at interactive frame rates. The volumetric data, stored in wavelet representation, is decoded and rendered on the fly and rendered utilizing graphics hardware.

These four previously presented rendering approaches [17, 1, 7, 8] employ a blocked data structure for handling the volumetric data-sets. The volume data-sets are divided into cubes with a width of  $2^n$  voxels. These cubes, called *cells* [1], *blocks* [8] or *macro-voxels* [17], are the *smallest data entities* which the presented compression and rendering algorithms are applied on. The methods presented in the papers are exclusively used in combination with rendering using ray-casting.

An approach exploiting the memory architecture of an Intel Pentium III system is presented by Knittel [9]. The data-set is stored and replicated in such a way, that during accesses to the data-set cache misses are reduced to a minimum. However, due to the specific storage method, the memory requirements are four times the size of the data-set. For large data-sets this method would be inadequate.

# 2.4 Data Reduction by Wavelet-Transformation and Compression

Rodler et al. [12] propose a wavelet based method for compressing volumetric data with little loss in quality allowing fast random access to individual voxels within the volume. It was possible to achieve very high compression rates with fairly fast random access.

Bajaj et al. [1] use wavelet transformation, for entropy encoding they present their own method. Guthe et al. [7, 8] use also wavelet transformation and various entropy coding methods: LZ77 [18], arithmetic coding and zero tree coding [15].

Many approaches [1, 12, 7, 8] employ a two stage compression method consisting of signal transformation and an entropy compression step. Additionally a quantization step is inserted between the two steps: For the transformation step, the wavelet transformation is widely used. For the entropy compression step, code-book based or tree based compression algorithms are used. Examples for code-book based algorithms are: LZW [16] and LZ77 [18]. Today LZ77 descendants are widely used in many compression tools (for example ZIP) and image formats (for example PNG). LZO [11], the compression algorithm used in this diploma thesis, is also based on LZ77. Tree-based compression algorithms are: zero trees [15] and its descendants like SPIHT [13]. The signal processing step combined with the quantization step is used for controlling the quality of the compression. It is possible to reduce the amount of required space for storing the data 1/100 with only a little loss of information.

# Chapter 3

# Computer System Issues

#### 3.1 Introduction

In the past years the discrepancy between processor and memory performance has significantly increased, even more, the discrepancy between CPU performance and mass storage access speed has dramatically diverged. This issue turns out to be a potential bottleneck for applications which require very fast access to large amounts of data. Volumetric data processing is prone to cause problems, since several algorithms require fast processing of large amounts of data.

Besides the discrepancy between the CPU and mass storage devices, another important issue arises with the complex design of current computer hardware: The hardware is highly optimized for sequential contiguous accesses to large chunks of data, which does not fit the way of processing of volumetric data requiring arbitrary accesses to data.

For many algorithms in the field of computer science, the device whereon the algorithm is implemented is not important. In contrast, since volumetric data processing requires efficient data transfer capabilities of all hardware components, it is of particular importance to investigate the properties of the computer hardware. In this chapter, each hardware component in the data processing path affecting the efficiency of it in some way, is surveyed.

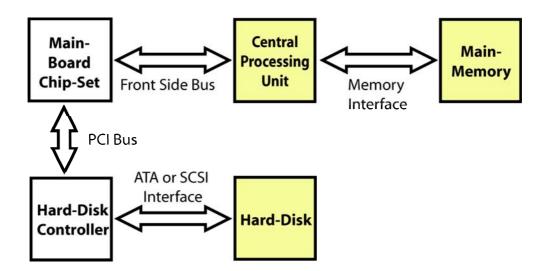

Figure 3.1: A computer system consists of three major components dealing with data: The CPU as data processing unit, the Main-Memory for volatile temporary data storage and the Hard-Disk for permanent data storage. Besides that, there is also some  $interconnect\ logic$  required, i.e. the  $Main-Board\ Chip-Set$  and the Hard-disk Controller, interconnecting these main components. The arrows denote a bidirectional communication interface between these components.

## 3.2 Data Processing Components

A computer system consists of three major components inherently dealing with data: The CPU as data processing unit, the main-memory for volatile temporary data storage and the hard-disk for permanent data storage. These three components are depicted in Figure 3.1

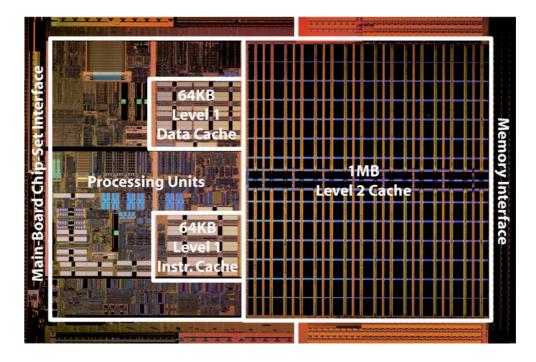

1. CPU: The CPU is the Central Processing Unit of a computer, consisting of the processing units, the level 1 and level 2 cache and external interfaces (see Figure 3.2). The processing units perform various operations on a set of registers, controlled by instructions. The level 1 cache, separated for data and instructions holds the data respective instructions which are actually processed. The level 2 cache holds copies of recently processed data of the main-memory.

- 2. Main-Memory: The main-memory is a volatile temporary data storage holding the data which is processed during the runtime of the computer system. The main-memory is accessed by the CPU through its caches.

- 3. Mass storage device: A common mass storage device is the so-called *hard-disk drive*. All storage devices have in common, that data can be permanently stored.

Beside these three main components, there is also some interconnecting logic, i.e. the main-board chip-set containing auxiliary system components like a real time clock and interfaces implementing several communication bus standards. Further additional components, like a hard-disk controller for controlling the communication between a device interconnect bus and the hard-disk drive, are required.

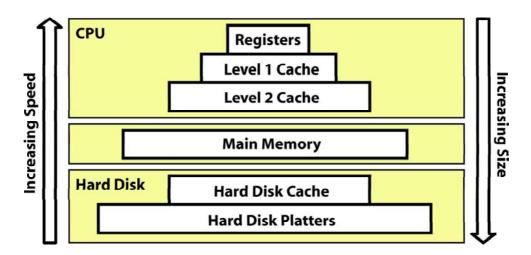

## 3.3 Memory Hierarchy

The memory of contemporary computers is structured in a hierarchy of successively larger, slower, and also cheaper memory levels (see Figure 3.3). The complexity of the hardware architecture incurs a penalty for programs which do not take optimal advantage of this hardware architecture. Disregarding the architectural peculiarities of the hardware results in an increased latency and reduced efficiency of data transfers. When developing efficient data processing algorithms it is very important to take a close look at the memory hierarchy. The hierarchy consists of successively larger but slower memory technology. Table 3.1 shows the memory specifications of a commodity computer.

## 3.3.1 Hierarchy Properties

The registers are the topmost level of the memory hierarchy which can hold data (see Figure 3.3). The data for the registers is transferred from the level 1 cache. The level 1 cache is used as temporary storage for instructions and data, making sure the processor has a steady supply of instructions and data

Figure 3.2: Structure of a modern CPU (AMD Opteron): Level 1 Cache (Data and Instructions), Level 2 Cache, Processing Units and external interfaces, i.e. the Memory Interface and the Main-Board Chip-Set Interface, are integrated on a single die. (The CPU image is taken from the AMD Digital Media Library)

| Level           | Latency    | Size        | Bandwidth            |

|-----------------|------------|-------------|----------------------|

| Register        | 1 - 3 ns   | 1KB         |                      |

| Level 1 cache   | 2 - 8 ns   | 8 - 128KB   | $20 \mathrm{GB/sec}$ |

| Level 2 cache   | 5 - 12 ns  | 0.5 - 8MB   | $10 \mathrm{GB/sec}$ |

| Main-memory     | 10 - 60 ns | 256 - 2GB   | 2GB/sec              |

| Hard-disk cache | 50 ns      | 2 - 8MB     | 200MB/sec            |

| Hard-disk       | 8 - 20 ms  | 100 - 300GB | 50MB/sec             |

Table 3.1: Memory hierarchy of modern computer systems. The memory hierarchy is structured top-down in successively larger but slower storage technology.

to process while new data is transferred from the main memory. As listed in Table 3.1 the common size of the level 1 cache is in the kilobyte range

Figure 3.3: The memory hierarchy is mapped onto the three data processing components (yellow boxes). The *CPU* contains the upmost three levels: *Registers, Level 1 Cache* and *Level 2 Cache*. The next level below is the *Main-Memory*, placed physically close to the CPU. The *Hard-Disk* is at the bottom level. It communicates through interconnect logic with the CPU. It can also have a cache.

with an access-time of few nanoseconds. The level 2 cache is the high speed memory caching the data of the main-memory. The size of the level 2 cache is several megabytes with an access-time around 10ns. The next level is the main-memory holding the actual data being processed. Its size is roughly 1000 times the size of the level 2 cache and is usually in the gigabyte range. The next level below is the mass storage device, usually a hard-disk drive. It also has a cache with a size in the megabyte range for faster access. The size of the hard-disk can be several hundred gigabytes.

Current operating systems support a virtual address space with paging which allows to extend the memory space onto the hard-disk. The file on the hard-disk holding the pages is called *swap file*.

Going up the cache hierarchy towards the CPU, caches get smaller and faster. In general, if the CPU issues an operation on a data item, the request is propagated down the memory hierarchy until the requested data is found. It is very time consuming if the data is often found in lower levels. This

is due to the propagation delay itself as well as to the back propagation of data through the complete hierarchy. For good performance, the number of accesses to the lower levels has to be reduced to an inevitable minimum. Therefore emphasis is put on efficient accessing strategies to the lower levels, like hard-disk and main-memory. Thus, the main focus lies in optimizing main-memory and hard-disk accesses in the following way:

- Loading data from lower levels only if required.

- Sequentially accessing data in memory and on hard-disk.

- Processing of data blocks smaller than the cache size.

#### 3.3.2 CPU

The memory of the CPU consists of: registers, level 1 cache and level 2 cache. In recent years, the level 1 cache and the level 2 cache are integrated together with the CPU on a single die as depicted in Figure 3.2. The short connections between the processing units and the caches dramatically reduces the propagation delay (the speed of signal propagation in silicon is around 20 centimeter per nanosecond), which results in very fast access times in the nanosecond range (see table 3.1.) to the level 1 cache and level 2 cache.

#### Registers

The registers hold single data words for immediate processing and are addressed directly by the CPU. The registers being accessed are encoded in the instructions. Registers are the fastest cache.

#### Level 1 Cache and Level 2 Cache

A cache is a highly efficient memory storage device. It holds copies of data blocks stored on its associated storage device in a lower memory hierarchy level.

In general, caches are hidden structures and therefore not directly controllable by software. Caches serve as a temporary storage for fast data accesses. Two issues are addressed with a cache at once: First, repeated direct accesses to its relatively slow associated storage device holding the actual data are avoided. Second, the efficiency of repeated access to the data is increased because of the short access latency of the cache. It is ensured that the data in the caches is always consistent with the data in the storage device. The only way to optimally utilize caches is accessing them in a pattern that the number of updates of the data in the cache from the actual storage device is reduced to a minimum. A situation, wherein a significant fraction of time is constantly used up by data replacements in the cache, is referred to as *cache thrashing*.

A cache is a relatively small memory holding temporary data. The memory is split up into small units, called *cache lines*, usually 32 or 64 bytes long. A cache line is synchronized only as a whole with the main-memory. Thus a cache consists usually of  $2^m$  cache lines with a cache line length of  $2^n$ . In direct mapped caches a location in main-memory of the size of the cache line is mapped exactly to a single cache line. The bits 0 to n-1 of the memory address are used as offset into the cache line, the bits n to n+m-1 are used to address the cache line itself. The remaining bits are stored as so-called tag bits in the cache. In a fully associative cache a memory location can be mapped to any cache line. This type of cache is seldom used because it is very complex to implement in hardware. A good compromise is a n-way set associative cache. The cache is organized in s sets of s cache lines. A memory location is mapped to one set. A direct mapped cache is an one-way set associative cache.

Since a cache line is updated only as a whole, even when one single byte is accessed, the whole cache line with a length of 32 or 64 bytes is updated. This is the reason for the degrading efficiency during cache thrashing.

The simple test code in Figure 3.4 shows, that the performance dramatically decreases if the memory is not sequentially accessed. Both triple nested loops do exactly the same: incrementing each field of the array by one. Theoretically the speed must be the same, but practically it is not. Experiments on a AMD 1.2 GHz CPU with 133 megahertz SDRAM with 64bit interface width (resulting in a theoretical bandwidth of 1 gigabyte per second) have shown,

that the sequential access is roughly 50 times faster than the non-sequential access.

```

int x,y,z;

// array size 16MB

char array[256][256][256];

// traversal in x,y,z order = total sequential access

for (z=0; z<256; z++)

for (y=0; y<256; y++)

for (x=0; x<256; x++)

array[z][y][x]++;

// traversal in z,y,x order = non-sequential access

for (x=0; x<256; x++)

for (y=0; y<256; y++)

for (z=0; z<256; z++)

array[z][y][x]++;</pre>

```

Figure 3.4: This simple code shows the runtime behavior of a cache by accessing a three dimensional array in two different ways.

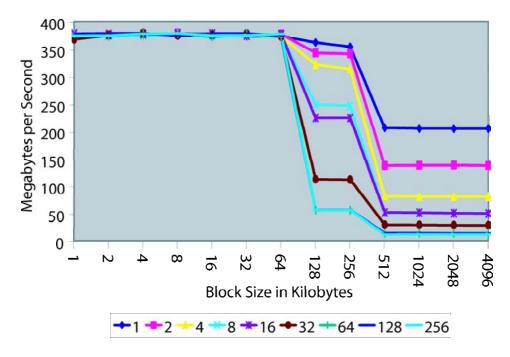

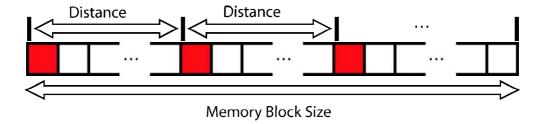

Figure 3.5 shows the results of the following test: A memory block of a certain size (block size in kilobytes) is allocated. Then single bytes are subsequently read from the memory block. After each byte-read an offset is added (distance) to the address. This scheme is depicted in Figure 3.6 It can be concluded, that as long the processed data fits into the L1 cache, the performance is not degraded regardless of the offset. The results for 64, 128 and 256 bytes distance are identical because the transfer capacity of the main-memory is exceeded: At each access a cache line of 64 bytes is updated. Since for each byte access a cache line of 64 bytes is updated, theoretically a maximum speed of 17 megabytes per second is possible, practically it was around 12 megabytes per second.

Figure 3.5: Sequential non-contiguous read access of single bytes with varying distance. The distances (offset added to the address after each byte read) are shown in the box at the bottom. The distance of 1 corresponds to a sequential contiguous access. This Figure clearly shows that the efficiency of accesses within the L1 cache, i.e. block size 64KB or smaller, is not degraded in any case. Results of an AMD CPU with 64KB level 1 cache and 256KB level 2 cache. The cache line length is 64 bytes. A graphical scheme of this test is depicted in Figure 3.6

### 3.3.3 Main-Memory

The history of memory is closely related to the history of the computer. From the beginning on a device storing bits over a longer period of time was required. Early random access memory (RAM) consisted of electron tubes or a wire grid with ferrite rings at the cross-overs. The development of modern memory started with the introduction of integrated circuits. The most common used memory type is the *Dynamic Random Access Memory* (DRAM). A simplified model of the DRAM architecture is depicted in Figure 3.7. DRAM is organized in the following way: A bit is stored in a memory cell.

Figure 3.6: Read test scheme. A memory block of a specific size is allocated and single bytes are read. After each read a specific distance is added to the address.

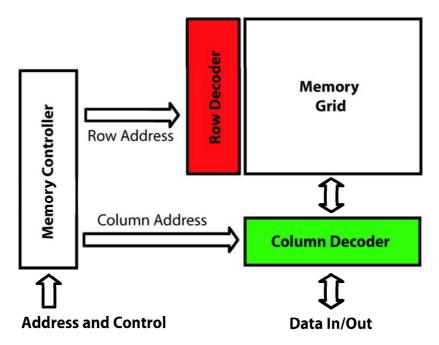

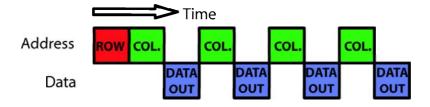

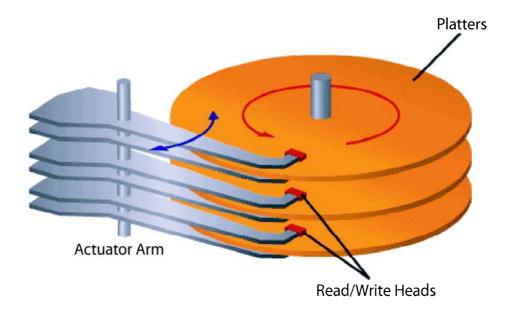

A memory cell consists of a small capacitor connected to a transistor. The memory cells are organized on a grid, also called storage array. The array is structured in rows and columns. The address supplied to the array by the memory controller is split up into two parts. the one part is used for row addressing and the other part for column addressing. A data word has a length of one bit. First the *Row Address* is send to the *Row Decoder*. It selects the desired row. Then each bit in the row is send to the *Column Decoder*. After that, the *Column Address* is supplied to the *Column Decoder* to select the desired bit, which can be read from the *Data I/O* interface (see Figure 3.8, *Random Access*).

For word lengths greater than one, multiple memory arrays are operating simultaneously.

Beside the structures storing the actual bits, additionally a refresh circuit, control and addressing unit is integrated on a single chip.

Since the charges volatilize over time, the charges have to be refreshed every few milliseconds. This is autonomously done by the memory controller. Also after reading, which destroys the contents of the memory cell, the affected charges are restored.

In the following paragraphs, several DRAM types are described in a chronological order, which is also an order with increasing performance.

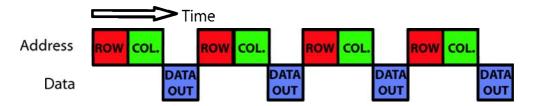

Ordinary DRAM is the simplest and also one of the oldest types of DRAM. Sequential accesses are supported by keeping the currently addressed row,

while supplying only different column addresses to the column decoder, which avoids extra row addressing (see Figure 3.8, Row Address Re-Use). This can be used to access a complete row by increasing the column address after each access.

Increasing the column address is automatically performed by the FPM-DRAM (Fast Page Mode DRAM). The DRAM automatically increments the column address, allowing the controller to access the next location without having to supply a new address. This allows a very efficient sequential access of a complete row, also called *page*. In consumer hardware the typical clock rates are 16 to 50 megahertz, with a word length of 16 or 32 bits yielding into a theoretical transfer bandwidth of 32 to 200 megabytes per second. The access latency time is around 60 to 100 nanoseconds.

EDO-DRAM (Extended Data Out DRAM) is similar to FPM-DRAM with the additional feature that a new access cycle can be started while keeping the data output of the previous cycle active. This allows a certain amount of overlap in operation, which improves the speed by roughly 5% (see Figure 3.8, Overlapping Addressing). Typical ratings are 50 to 66 megahertz with a word length of 32 bits yielding in a theoretical bandwidth of up-to 266 megabytes per second. The access latency time is around 40 to 60 nanoseconds.

Synchronous DRAM (SDRAM) is an improved type of DRAM. While DRAM reacts immediately to changes in its control inputs, SDRAM has a synchronous interface, meaning that its signal I/O is synchronized with a clock signal. This allows the SDRAM to have a more complex pattern of operation than plain DRAM. Accesses to the SDRAM are controlled by sequences of commands allowing pipelining, i.e. overlapping of read or write sequences. Typical ratings are 66 to 133 megahertz with a word length of 64 bits yielding in a theoretical bandwidth of up-to 1 gigabyte per second. The access latency time is 10 nanoseconds.

Doubled Data Rate SDRAM (DDR-SDRAM) is a later development of SDRAM. Plain SDRAM acts on rising edge of the clock signal. DDR-SDRAM acts on the rising and the falling edge thereby halving the required clock rate for a given data transfer. Common configurations support a 128bit data word width with 266 to 400 million words per second, resulting in a theoretical

bandwidth up to 6.4 gigabytes per second.

Figure 3.7: Basic memory architecture: The input data is the address and control (read or write access) and the output (read access) respective input (write access) is the data for the specified address. The bits are stored in memory cells organized in a *Memory Grid*. The *Address* is split into a *Row Address* and a *Column Address*. First the *Row Address* is sent to the *Memory Grid*, then the whole row, also called page, is sent to the *Column Decoder* which selects the desired column.

### 3.3.4 Mass Storage Device: Hard-Disk Drive

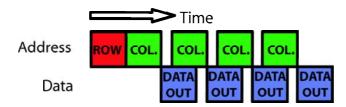

The most commonly used mass storage device is the so-called hard-disk drive. It consists of a rotating stack of platters made of aluminium or ceramics coated with a magnetic material. A moveable lever called actuator arm holds the heads which perform write and read actions on the platters (see Figure 3.9). The rotation speed was initially 3600 rpm in the early days, later 4500 rpm and 5400 rpm, and nowadays consumer hard-disk drives have a rotation speed of 7200 rpm. High-end hard-disk drives have a speed from

#### **Random Access**

#### **Row Address Re-Use (FPM-DRAM)**

#### **Overlapping Addressing (EDO-DRAM)**

Figure 3.8: Memory read sequences: For reading data words randomly, first the row and subsequently only column addresses have to be send for each word (first sequence). Sequential reads: With FPM-DRAM the sequential reads have been optimized by reusing the column address, for example automatic column address increment (second sequence). Later, overlapping the requests (third sequence) was introduced with EDO-DRAM.

10000 rpm up-to 15000 rpm. At the time of writing this diploma thesis the common size is around 200 gigabytes. The data density is around 600000 bits per inch on a track, and 100000 tracks per inch on a platter. this results roughly in a data density of 60 gigabits per square inch: In a 200 gigabyte disk drive, the stack holds two platters (in total 4 sides), each of them holding 50 gigabytes. Reading and writing is performed by accessing the bits

on a track surpassing the head. The theoretical maximum transfer speed is calculated as follows: A track has an average length of 16 cm (depending on its radius the length ranges from 7 to 25 cm). Therefore it holds roughly 4 megabits of data. The maximum transfer speed at 7200 rpm (120 rounds per second) is about 480 megabits per second or 60 megabytes per second. The track to track seek time is around 1ms, a random track seek is 9ms average. These properties of a hard-disk lead to the conclusion, that only sequential contiguous accesses can utilize the hard-disk architecture optimally. Therefore, for out-of-core approaches it is desirable to sequentially access the hard-disk by the way of contiguous data blocks.

Figure 3.9: Hard-disk drive scheme: A moveable lever called *Actuator Arm* holds the *Read/Write Heads* which perform write and read actions on the *Platters*. The *Platters* are made of aluminium or ceramics coated with a magnetic material. Several *Platters* are mounted on a rotating spindle.

### 3.4 Summary

Many common memory architectures have one feature in common: they are optimized for sequential contiguous accesses. Each memory level, starting at the top with the level 1 cache down to the hard-disk is designed so that sequential accesses are the most optimal way to access the data. A sequential access is simply an access to a contiguous block of data with specific starting address and length. A reading access results in a data transfer from one memory hierarchy level to the levels above. The propagation of the data bottom up through the hierarchy is crucial. In volumetric data processing fast read accesses are very important to be efficient. Most memory hardware support sequential contiguous accesses by so-called burst transfers. After the starting address, and optionally if supported by the architecture the length of the desired block, has been sent to the memory, a whole sequence of words is transferred at once instead of a single word. A word is the smallest transferable element in a memory. Thus it is important to exploit this behavior when accessing the main-memory or any mass storage device. This issue is discussed later in detail in the section about the optimal brick size.

Irregular accesses cause a significant degradation of performance if memory hierarchy levels are affected which are sensitive to non sequential accesses. The affected levels are usually the main-memory and the mass storage devices. As long as no update of the caches through those levels is constantly required, no significant performance decrease occurs.

# Chapter 4

# **Block Volume Memory Layout**

This chapter addresses the issue, that if an algorithm accesses a memory or mass storage device in an irregular pattern or, more simply speaking, not in a sequential contiguous fashion, the performance drastically degrades. Methods overcoming this issue by exploiting the advantages of the current computer architecture hierarchy are presented. The intention of these methods is to allow irregular accesses while maintaining sequential accesses for performance reasons.

First, volumetric data in general and its properties are reviewed. Second, the sequential volume, a commonly used layout for volumetric data, is introduced and discussed. Further, the block volume concept remedying several deficiencies of the sequential volume and taking concepts from the previous section into account is presented. Finally, the volume processing hierarchy, a high-level concept for accessing the block volume is introduced.

## 4.1 Volumetric Data Properties

In this section, several characteristics of volumetric data, which can be exploited by various algorithms, are discussed. The focus is put on computer tomography data, but it does not preclude that these characteristics apply also to other types of volumetric data, such as magnetic resonance imaging data, simulation data, etc.

Many algorithms access only a fraction of the volumetric data-set. This fraction can be bounded in the spacial domain or in value domain. For example such a fraction in spacial domain is a block shaped sub-set of the whole volume data-set. In value domain such a fraction consists of all voxels in a certain value range.

#### 4.1.1 Non-Relevant Data

Non-relevant data is, as its term denotes, not relevant for the result of an algorithm. It often degrades the performance of an algorithm due to unnecessary processing. Additional data structures to reduce accesses to non-relevant data can considerably increase the performance of an algorithm.

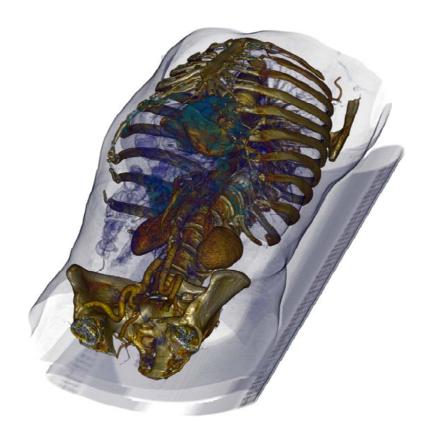

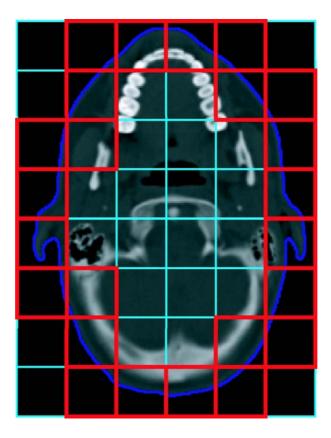

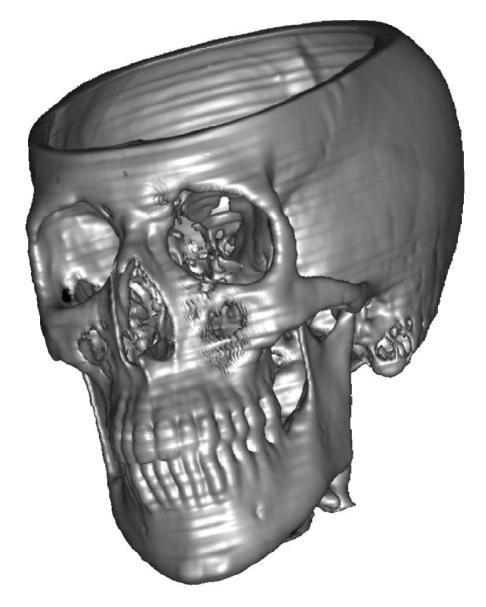

An example of an algorithm requiring just a fraction of data in value domain is the marching cubes [10] surface extraction method. It only requires the voxels close to the surface, represented by a fixed predefined value, to construct the polygonal mesh of the surface. Figure 4.1 shows the classification of blocks into relevant and non-relevant blocks for surface extraction. If an implementation of this algorithm uses a sequential layout in a slice-by-slice manner, many voxels would be read from the mass-storage device, which do not contribute to the surface construction.

Typical data-structures to determine relevant voxels are tree-based search structures forming a hierarchical search space with increasing granularity. Large partitions of the search space can be omitted in the higher levels which significantly reduces the size of the search space. With these structures it is possible to efficiently exclude non-relevant data. Time-expensive memory or mass-storage accesses are avoided and the efficiency of the algorithms significantly improves.

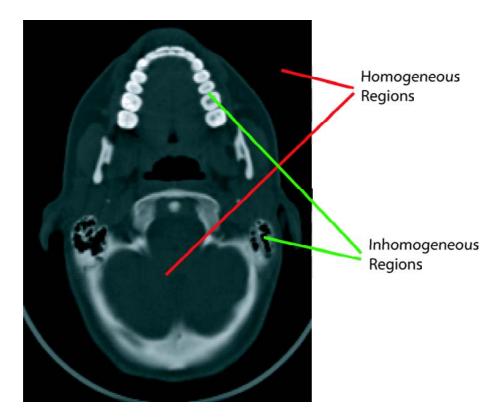

As shown in Figure 4.2 volume data-sets acquired from computer tomography imaging devices contain large regions of voxels with similar values, representing homogeneous material in the scanned objects. For example, soft tissue or air. In many cases these regions are likely to be non-relevant data. Therefore search structures mentioned above can be used to identify these regions. For example, a simple octree structure can be used: Each

node contains the minimum and maximum density value of its sub-nodes. Assume an algorithm processing density values in a certain predefined range. If the algorithm encounters a node whose minimum-maximum range does not overlap with the range of the algorithm then the whole sub-tree can be omitted.

Figure 4.1: Classification of blocks into relevant (red) and non-relevant (cyan) blocks for surface extraction. The intended surface is highlighted (blue).

### 4.1.2 Memory Access

All memory architectures have one feature in common: they are optimized for sequential contiguous access. Each memory level, starting at the top with the level 1 cache down to the hard-disk is designed so that sequential accesses

Figure 4.2: Types of regions in a data-set. *Homogeneous Regions* contain less information and *Inhomogeneous Regions* contain more information.

are the most optimal pattern to access the data. A sequential access is simply an access to a contiguous block of data with specific starting address and length. A read-access results in a data transfer from one memory hierarchy level to the levels above. The propagation of the data bottom up through the hierarchy is crucial. In volumetric data processing fast read access is very important in order to achieve high performance.

Contiguous sequential accesses are supported by most of the memory hardware by so-called *burst transfers*. After the starting address, and optionally, if supported by the architecture, the length of the desired block in words, has been sent to the memory controller, a whole sequence of words is transferred at once instead of a single word per addressing action.

Irregular accesses constantly trigger cache updates. This leads to a degradation of performance if memory hierarchy levels are affected which are sensitive to non-sequential accesses. The affected levels are usually the main-memory and the mass storage devices. As long no update of the caches through those levels is constantly required, no significant performance decrease occurs. Thus it is important to exploit this sequential access behavior when accessing the main-memory or any mass storage device.

#### 4.1.3 Out-of-Core Processing

Assume a 4 gigabyte data-set to be processed and the following system available: 1 gigabyte of physical memory available for storing volumetric data, and a hard-disk holding the data with an interface speed of 100 megabytes per second. Other limiting factors (i.e. memory speed, CPU speed) are neglected. In this case it is impossible to keep the complete data-set in memory, therefore the complete data-set has to be loaded piecewise from the hard-disk during processing. In the theoretically best case the data-set can be processed in 40 seconds (neglecting all latencies and limiting factors, except the hard-disk interface speed). The processing time and memory requirements can be reduced.

Processing of relevant data. Most algorithms require only a fraction of the volumetric data-set. It is favorable to retrieve only the required data from the storage device which is relevant for the result of the algorithm. Auxiliary search structures are used to efficiently locate the needed data in spacial and value domain. This approach is similar to the sparse traversal in [7].

Compressed data. Effectively more information can be transferred over an interface in compressed form in the same time compared to uncompressed data. Ideally the sum of the transfer time of the compressed data and its decompression time should be smaller than the transfer time of uncompressed data to achieve a speed increase. Preliminary tests of compressing computer tomography data with the LZO-compression [11] showed that the data can be reduced by 30 to 50 percent and decompressed with a speed roughly twice the hard-disk interface speed.

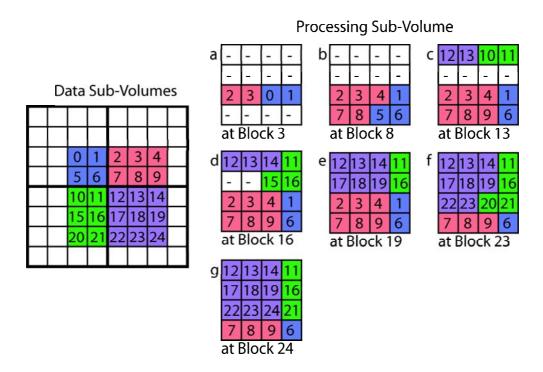

Efficient resource usage. If a data-set does not fit into the main-memory as a whole, the memory must be reused for other portions of the data-set. An efficient way to achieve that is to partition the data-set into small entities which can be retrieved from the storage device as contiguous chunks of data. Ideally such a partition should consist of spatially bounded data. Such partitions can be slices (i.e. data in a plane) or small sub-volumes (i.e. data in cubically regions). In the following such a partition will be referred to as smallest available entity. This approach is similar to the segments, pages and replacement policy in [5]

#### 4.1.4 Application Examples

The sequential volume allows an effective sequential line-by-line respective slice-by-slice processing of the data. Therefore this layout is very efficient for algorithms which process volumetric data in this manner.

An example for an algorithm processing volumetric data slice by slice is the well-known surface extraction method called  $Marching\ Cubes\ [10]$ . Algorithms processing single voxels like thresholding or windowing-functions also benefit from the sequential layout, because thy process the data sequentially. The most profoundly disadvantage of this layout is, that the effectiveness degrades dramatically when an algorithm requires a random access pattern to the data or, more simply, requires access in a different order than in a slice-by-slice or line-by-line manner. For example, accessing slices in the xz-plane requires processing of single lines across the entire data-set. Even worse, accesses to slices in the yz-plane require processing of single voxels, which totally compromise the caching mechanisms of the hardware, resulting in massive  $cache\ thrashing$ .

Many algorithms require accesses not only to single voxels but additionally to their neighborhood, i.e. a three-dimensional region around a voxel. These algorithms are also affected by cache thrashing. For example, such algorithms are gradient-calculations and general three dimensional signal processing operations, like filters and transformations.

#### 4.2 Block Volume

#### 4.2.1 Sequential Volume

The sequential volume has arisen in the 1970s with the upcoming of three dimensional medical imaging systems. The data acquired by such an imaging device is stored as a sequence of two dimensional images. These images itself consist of a sequence of lines which are itself sequences of single data values. The sequence of images can be interpreted as a three dimensional volume block where the values are stored sequentially starting with the first line of the first slice going to the last line of the last slice.

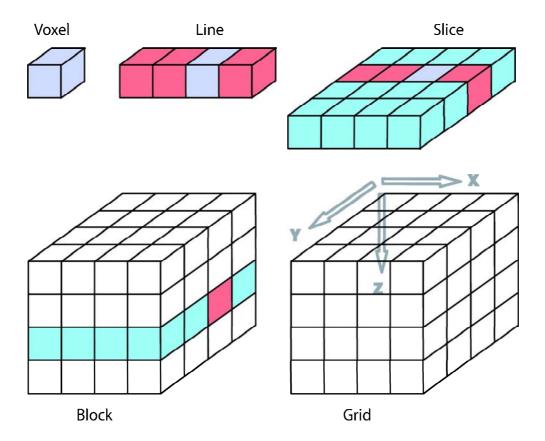

The sequential volume is structured as follows: The smallest data element in a sequential volume is a *voxel*. A sequence of voxels forms a *line*. A sequence of lines constitute a *slice*. A stack of slices constitute a *volume*. These structures and its relations are shown in Figure 4.3:

- Grid. A volume grid is a discrete three dimensional structure of a predefined size in a three dimensional regular orthogonal coordinate system. For each voxel it establishes a relation to a position in space represented by the a grid point.

- Voxel. A voxel consists of a vector, a sequence of values assigned to a position in a volume grid. For example, in CT data-sets this vector contains a single unsigned 12 bit value.

- Line. A line is a sequence of voxels along an axis of the volume grid. If not identified otherwise a line is parallel to x-axis of a slice parallel to the xy-plane.

- Slice. A slice consists of a number of lines. If not identified otherwise a slice is parallel to the xy-plane.

- Block. A volume block consists of a stack of slices along the z-axis of the volume grid.

Figure 4.3: The sequential volume layout. A *Block* is a set of *Voxels* stored according to a Grid. A *Block* consists of a stack of *Slices*. A *Slice* consists of a *Line* of *Voxels*.

#### 4.2.2 Motivation of the Block Volume

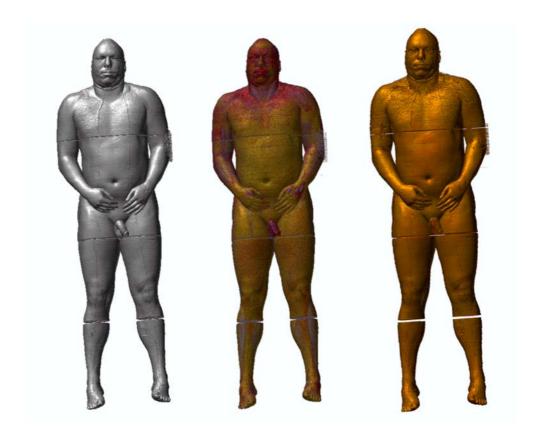

In Figure 4.4 images of a large volumetric data-set (1.6 gigabyte *Visible Male* data-set) are shown. On common computers, data-sets of this size can be easily stored on the hard-disk, but they often exceed their physical memory resources. Even larger data-sets can exceed the capabilities of all components of the computer system. For example, the address space of a CPU can be easily exceeded: If a CPU has a 32 bit address space it is not possible to directly address more than 4 gigabytes of memory.

Simply dividing the data-set into smaller manageable independent sub-sets is the most straight-forward way to circumvent this issue. Only one sub-set

Figure 4.4: Three images of the *Visible Male*. A 1.6 gigabytes volumetric data-set.

is held in memory while the others are remaining on the hard-disk. This would be a reasonable solution if the algorithm can be applied on manageable sub-sets such that the results of each processed sub-set can be merged together easily to get the same result as processing the data-set as a whole. Especially for algorithms relying on common global properties, for example a minimum cost for the region growing algorithm, this is not easily achievable. Another way would be the compression of the data-set to reduce its memory requirements. This requires methods to directly operate on compressed data. However, the additional processing overhead, especially if random access is required, can be considerably high.

A good method would be a trade-off between speed and memory require-

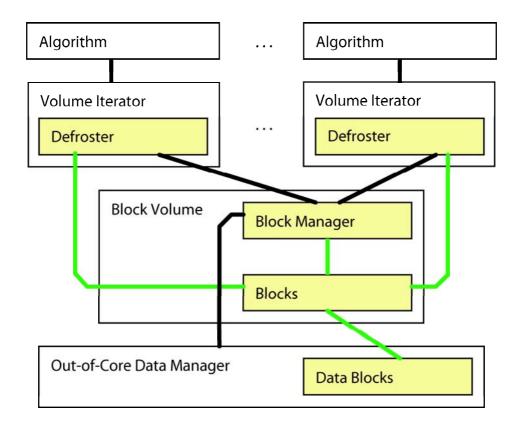

ments. The data-set is divided into sub-sets that can be easily accessed through an interface that hides the actual data management from the algorithm by providing a clear generic interface for data access. The interface should allow random access to the data in a simple and efficient way. Additionally it should support fast compression to reduce memory requirements and better utilization of the hard-disk interface. The subdivision combined with compression allows storing the data-set in compressed form on a hard-disk and in uncompressed form in memory for processing.

Based on this concept an approach for managing large volumetric data-sets is introduced.

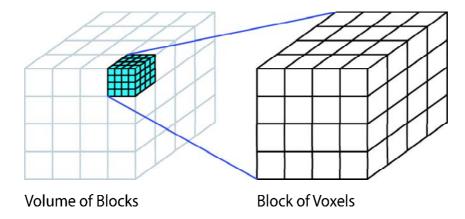

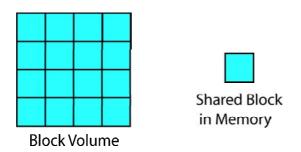

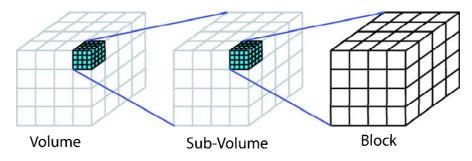

Based on these concepts, a data structure for storing volumetric data, the block volume is introduced.

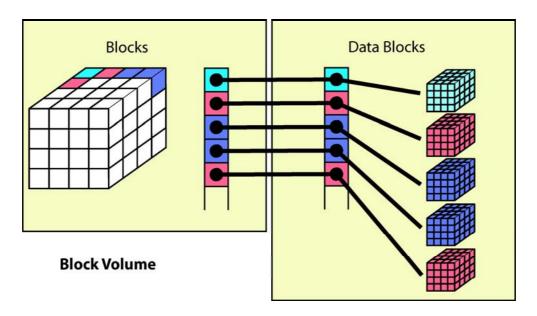

### 4.2.3 Contiguous Block Volume

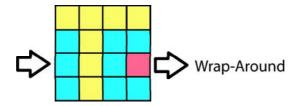

A block volume is a two level application of the sequential layout. The volumetric data-set is sub-divided in sequentially organized fixed-size data blocks. Also the data blocks are internally organized according to the sequential layout (see Figure 4.5).

A contiguous block volume provides a different way to store volumetric data. It has a higher processing overhead than a sequential volume, but its efficient cache usage easily compensates this overhead. Actually according to Grimm et al. [6] the data can be processed multiple times faster than in a sequential volume. The memory requirements are similar to the sequential volume.

The contiguous block volume demands a more complex addressing scheme compared to a simple sequential volume. The addressing scheme is described in one of the following sections. The intended purpose of the contiguous block volume is to provide an efficient data access. This is achieved by a data block size allowing efficient cache usage and an efficient addressing scheme. The concept of the contiguous block volume and its addressing scheme has been introduced by Grimm et al. [6].

Figure 4.5: The volume data-set is organized in a two level sequential layout: The volume consists of sequentially ordered blocks, which themselves consist of sequentially ordered voxels.

#### Optimal Data Block Size

The data block size should be selected in favor of fast address calculation for data access and optimal cache usage. If the width of the data block is a power of 2, the address calculation can be efficiently done with bit-manipulating and shifting operations only.

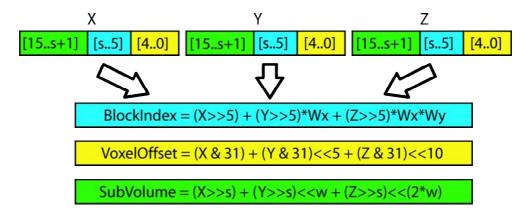

The data block size is determined in such a way, that at least one, or even better, several data blocks should fit into the level 2 cache. Since solely 16 bit data is processed, the formula for the size calculation is:  $DataBlockSize := 2*(2^n)^3bytes$ . Thus meaningful sizes are: 1 kilobyte (n=3), 8 kilobytes (n=4), 64 kilobytes (n=5), 512 kilobytes (n=6) and 4096 kilobytes (n=7). It was found out by Grimm et al. [6], that on a CPU with a level 2 cache size in the 0.5 megabyte to 1 megabyte range a data block size of 64 kilobytes is the most efficient size. Therefore a data block of  $32^3(n=5)$  voxels is used in the implementation. Each voxel consists of a 16 bit unsigned value. Thus each data block has the size of 64 kilobytes.

#### Addressing Scheme

For accessing a voxel in a volumetric data-set, its location in memory, the address, has to be calculated. The address is derived from the position of the voxel in the three dimensional space. In the sequential layout the voxel address is simply a linear combination of the components of the position of the voxel. For the block volume a two step addressing scheme is introduced, which is described in the next section.

Since address calculations are performed very frequently, therefore the most important issue is simply *speed*. All steps in the address calculation follow this requirement. The calculations are done in a way that time-consuming CPU instructions like branching instructions (jumps, loops) and instructions associated with time consuming pipeline flushes are avoided. Also complex mathematical calculations (divisions, multiplications) are avoided. The calculations are designed to exploit the fastest instructions like simple arithmetic (addition, subtraction), bit-manipulation and shifting operations. Also no look-up tables are used to minimize the number of relatively slow memory accesses.

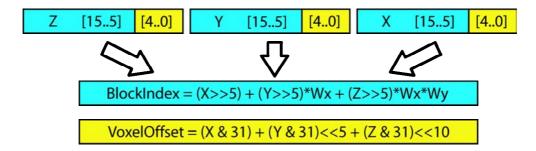

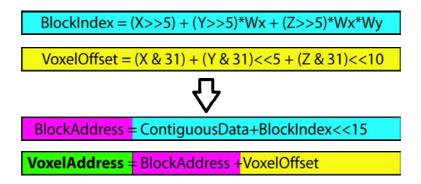

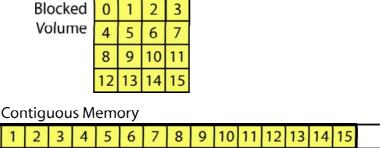

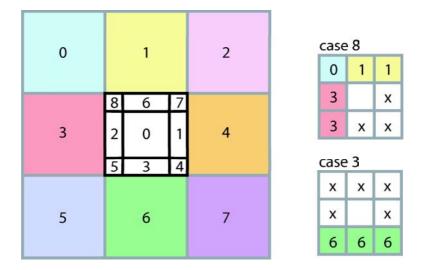

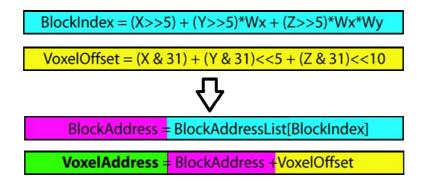

Absolute Addressing The absolute address is the address directly derived from the voxel position in the three dimensional space. For the block volume a two step addressing scheme is introduced: In the first step (see Figure 4.6) the block index and the voxel offset are calculated from the position. In the second step (see Figure 4.7) the voxel address is calculated. Since in the contiguous block volume the data blocks are sequentially stored in a large contiguous memory area (see Figure 4.8), the data block address can be directly derived from the block index by a simple shift operation.

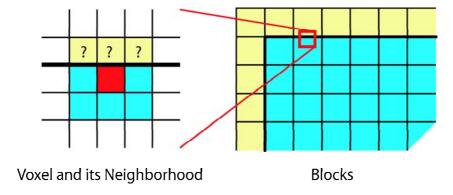

Relative Addressing Once if the absolute address for accessing a specific voxel, the *active voxel*, is calculated, it is advantageous to have an efficient method to access the neighboring voxels. In this section an approach to efficiently access the 26-neighborhood around a voxel is presented. The neighborhood is the 3x3x3 cube of voxels with the *active voxel* in the center. The 3x3x3 cube, where the *active voxel* lies in, is called the *active cube*.

Figure 4.6: block index and voxel offset calculation. For the voxel offset, only the 5 lowest bits are used, for the block index the bits above the 5 lowest bits are used.

Figure 4.7: Absolute voxel address calculation for contiguous memory.

For each voxel in a block there are 26 neighbors. The absolute addresses of the neighbors are calculated by simply adding an offset to the address of the active voxel. This offset is called the *relative address*. The relative address is the difference between the the absolute address of the active voxel and one of its 26 neighbors.

Storing a list, the so-called *neighbor-list*, containing 26 relative addresses to the neighboring voxels, for each voxel is not desirable. It would result in a look-up table with  $32^3 * 26 = 851968$  entries.

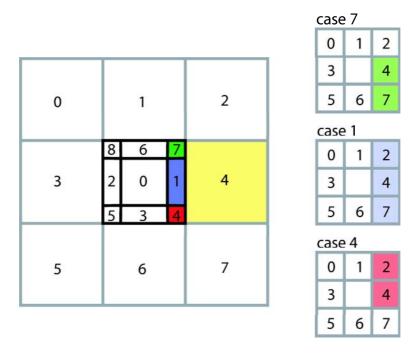

Fortunately the neighbor-lists can be classified into 27 different *neighbor* cases: The trivial case is, that all neighboring voxels are in the same block. This applies for the inner voxels of a block. For the border voxels, the re-

0

Figure 4.8: Data organization in contiguous memory. The blocks are ordered sequentially. The block index can be directly used for data block address calculation. The thick box denotes the memory areas allocated through the memory manager.

maining 26 cases apply. In each case the 26 relative addresses are identical for each voxel within the case. Ultimately the neighbor look-up table consists of 27 lists with 26 entries each, in total 702 entries. Storing the entries as 4 byte integers results in a neighbor look-up table of the size of 2808 bytes. This list fits and remains in the cache all the time due to frequent accesses. Therefore the access is very fast. In the contiguous block volume the data blocks are sequentially stored in a large contiguous memory block. Due to this layout the relative distances between a data block and its 26 neighbors are the same for each data block, so only one global neighbor look-up table is necessary.

Neighbor Case Determination Each neighbor case is denoted by a case index. The case index is derived from the position within the data block. For the one dimensional space there are only 3 cases: most left voxel, inner voxels and most right voxel. For the inner voxels addressing neighboring voxels is straightforward: each neighbor voxel lies within the same block as the active voxel. But for the left most voxel, its left neighbor lies in a completely different block, i.e. the left neighboring block of the active block. Analogous is this case for the right most voxel: The right neighbor voxel of this voxel lies in the right neighbor block.

Formula (4.1) depicts the *case index function*. In the calculation only simple arithmetic, bit-manipulation and shifting operations are used. All possible function values are shown in Table 4.1

$$CaseIndex_{dim} = ((((((Position_{dim}\&31) - 1)\&63)|1) + 1) >> 5)$$

(4.1)

The position value is first masked with 31 to get the position within the data block. Then the index is calculated from this local position. Table 4.1 shows all possible function values.

| $Position_{dim}$ | $CaseIndex_{dim}$ |

|------------------|-------------------|

| 0                | 2                 |

| 130              | 0                 |

| 31               | 1                 |

Table 4.1: All possible values of the case index function for a data block width of 32 voxels.

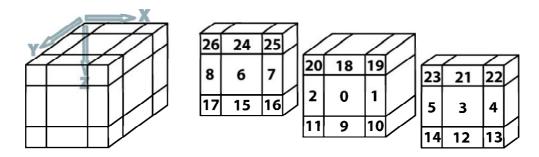

The case determination can be extended for n dimensions, resulting in  $3^n$  cases. The case index for the three dimensional space are calculated as follows: for each axis (i.e. x,y and z) the one dimensional case index is calculated (data block size  $32^3$ ) from the absolute position in the volume data-set. Since the range of function values of the one dimensional case index function is limited to 0..2, the three dimensional case index is simply derived as depicted in formula (4.2). Figure 4.9 shows all indices assigned to their position on a cube. In Figure 4.10 the cases and two entries of the neighbor-list are depicted for the two dimensional case.

$$CaseIndex = CaseIndex_z * 9 + CaseIndex_y * 3 + CaseIndex_x$$

(4.2)

Figure 4.9: The 27 case indices calculated from the case index formula (4.2).

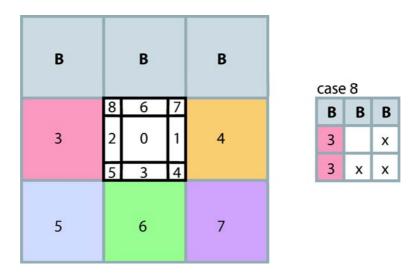

Figure 4.10: 9 different cases in two dimensional space. Each case has 8 entries (one for each neighbor). On the right there are sample tables of cases 8 and 3. The tables show in which neighbor block the neighboring voxel can be found. x denotes that the neighbor is in the same block.

#### Border Issue

With the relative neighbor addressing scheme a new issue is introduced, which affects the voxels at the volume border (see Figure 4.11). The relative address is calculated based on the addresses of the neighboring blocks, but at the border for some of the cases (see Figure 4.10) some neighboring blocks are missing.

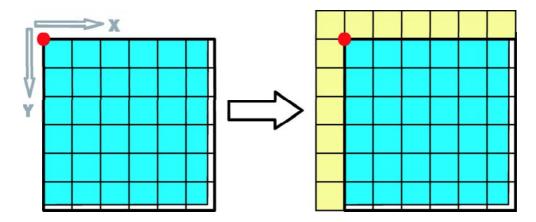

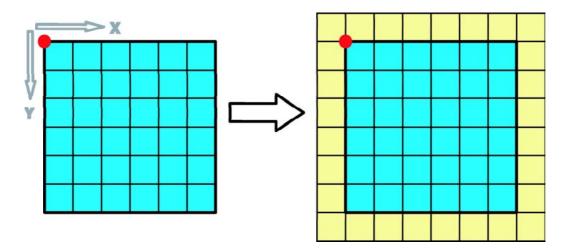

This issue is solved by adding extra border blocks. This increases the size of the volume of the original size of  $X \times Y \times Z$  blocks to a minimum size of  $(X+1) \times (Y+1) \times (Z+1)$  blocks and a maximum size of  $(X+2) \times (Y+2) \times (Z+2)$  blocks as depicted in Figure 4.12 and Figure 4.13.

In general only adding border blocks at three sides of the volume block is sufficient, because the volume data does not fill up all blocks at the border (see Figure 4.12). In certain cases, i.e. the width of the volume is a multiple of 32 voxels (block width), which in the volumetric data-sets completely fills up blocks at the border, border blocks at up to additional 3 sides of the volume block are required as depicted in Figure 4.13.

Figure 4.11: The voxel (red) is located at the border of a block which is also at the border of the volume. Also for such border voxels a relative neighbor addressing is required. It this case some of the neighboring voxels (denoted by "?") are located in a non-existing neighbor block.

Impact on the absolute addressing. The calculation of the block address is only affected marginaly by adding border blocks: The width variables

(holding the width of the volume in blocks)  $W_x$ ,  $W_y$ ,  $W_z$  are replaced by the width variables  $W_x'$ ,  $W_y'$ ,  $W_z'$  which contain the original values  $W_x$ ,  $W_y$ ,  $W_z$  increased by 1 or 2 (the additional borders). Further to the block index an offset  $W_x' * W_y' + W_x' + 1$  (i.e. the relative address of the first block containing volume data) is added. The voxel offset calculation is not modified because the bits which are relevant for the voxel offset are not affected by the border blocks.

Impact on the relative addressing. The adding of the border has no effect on the relative addressing scheme since it operates only locally within a block.

Figure 4.12: If the volume data does not fill up the data blocks completely on the right and/or bottom border, then only border data blocks at the left and top have to be added. The red dot denotes the origin of the coordinate system.

# 4.2.4 Fragmented Block Volume

In many cases during runtime the memory manager of an operating system is not able to allocate a contiguous memory block for storing the volumetric data, even though enough memory would be available. This is due to the fragmentation of the virtual address space during runtime. A solution to

Figure 4.13: If the volume data fills up the data blocks completely on the right and/or bottom border, then border data blocks at all borders have to be added. The red dot denotes the origin of the coordinate system.

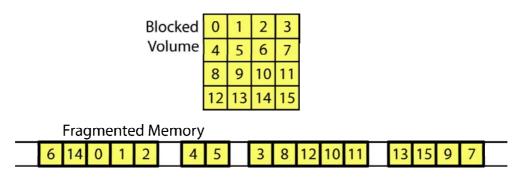

that problem is to split up the block volume in smaller pieces. To achieve that the data blocks are allowed to be irregularly ordered in virtual memory. The type of block volume is called *fragmented block volume*.

**Absolute Addressing** Instead of directly deriving the data block address from the block index, the data block address is looked up in a data block address list, see Figure 4.14 in the second calculation step. The organization of the data blocks in virtual memory is depicted in Figure 4.15.

Relative Addressing Basically the relative addressing scheme stays unmodified. Since in the fragmented block volume the data blocks are irregularly ordered, a single global neighbor look-up table is not sufficient because the relative position of the neighboring data blocks differs for each data block. Thus for each data block an own neighbor look-up table has to be maintained. This increases the overall memory requirement by 4.3% (64 kilobytes data + 2.8 kilobytes look-up table). As discussed later, this additional memory requirement can be quite large for large data-sets.

Figure 4.14: Absolute voxel address calculation for fragmented memory.

Figure 4.15: Data organization in fragmented memory. The blocks are irregularly ordered. The block index is used as index into a list containing the actual data block addresses. The thick border denotes the memory areas allocated through the memory manager.

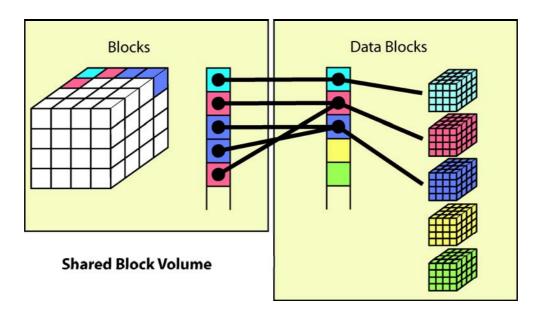

#### 4.2.5 Shared Block Volume

In the previous sections the contiguous and the *fragmented block volume* have been introduced. They provide an efficient access to the data and utilize memory space efficiently, but their memory requirements are not reduced, although it is an important issue for handling large data-sets.

Many data-sets contain large homogeneous regions, i.e. the border blocks or homogeneous regions (for example air) around a scanned object. These blocks contain the same data. Also when creating an large empty block volume filled with zero, all blocks contain the same value. Storing "empty" space

Figure 4.16: The *shared block volume*. In the *shared block volume* the mapping between the *Blocks* and the *Data Blocks* is a many-to-one mapping.

is not feasible, so actually the data of only one block is stored and is shared among the blocks containing the same data.

A step towards lower memory demands is the *shared block volume*. A *shared block volume* is an extension of the *fragmented block volume*.

In this concept a data block is extended in the following way: The block volume consists of blocks, which are references of data blocks: A block references exactly one data block, whereas a data block can be referenced, i.e. shared, by several blocks (see Figure 4.16). A fragmented block volume can be interpreted as a special case of a shared block volume: Each data block is referenced by exactly one block (see Figure 4.17).

#### **Data Handling**

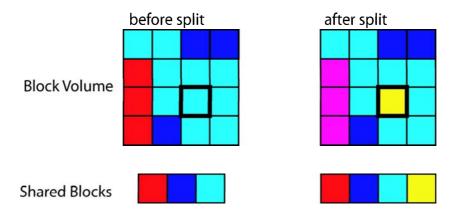

At creation time, a *shared block volume* is empty: All voxels contain the density value zero, therefore each block contains the same values, thus only one data block is necessary for representing the data of all blocks so one data block is shared by all blocks (see Figure 4.18).

Figure 4.17: The block volume. In the contiguous or fragmented block volume there is a one-to-one mapping between Blocks and  $Data\ Blocks$ .

Figure 4.18: A shared block volume at initialization time. A single data block is shared by all blocks.

Figure 4.19: A shared block volume at split. A block is modified (thick border). A new block is created holding the modified block (yellow block).

Data Block Split If a new value is written to a data block, which differs from the value at the current location, then a replica of this data block is generated. To this replicated data block the new value is written at the desired location. First the data block is shared by n blocks, after this step the data block is shared by n-1 blocks, and the modified data held by the replicated data block is shared by one block (see Figure 4.19).

Block Data Merge If a set of m blocks are sharing a data block and a set of n blocks are sharing another data block, both sets are disjunct, but the data blocks contain identical data, both sets can be merged. One memory location containing one data block can be freed and the other data block is shared then by n + m blocks. A merge requires comparing one data block with all other data blocks on voxel basis, which is computationally expensive, therefore it should be applied when no time-critical access to the volume occurs.

#### Addressing Issues

The shared block volume is basically a fragmented block volume, therefore each block has a neighbor look-up table. In a shared block volume where the addresses of the neighboring data blocks change during runtime, the neighbor

look-up tables of the affected blocks have to be updated to ensure consistent addressing of the data blocks. This achieved by using an update look-up table containing for each neighbor the fields of the neighbor look-up table to be updated.

If the address to a data block is changed by a data block split or a data block merge, then the neighbor look-up table of the block (i.e. the center block of a 3x3x3 cube of blocks) itself and its 26 neighbors have to be updated according to the changed address. For the center block the offset between the addresses of the old data block and the new data block is added to each entry in the neighbor look-up table. For each neighboring block, only those cases are updated, which in the center block is addressed.

Figure 4.20 shows the relation between the addressing and the *update look-up table* for updating the *neighbor look-up table*. For 2D the *update look-up table* contains 4 \* 1 + 4 \* 7 = 32 and for 3D 8 \* 1 + 12 \* 7 + 6 \* 49 = 386 entries.

#### **Border Handling**

In the shared block volume, no additional border blocks are added. Instead a special border data block is provided for simulating the border. Instead of having extra blocks as in Figure 4.10 these data blocks are replaced by this special border data block at the according position as depicted in Figure 4.21.

# 4.2.6 Compressed Shared Block Volume

For data-sets with large homogeneous regions the *shared block volume* reduces the memory requirements significantly. Also having an extremely large volume initially does not require much memory because one data block is shared among all blocks in the block volume. The memory requirements can be further reduced with the utilization of compression methods.

Up-to now, only data structures storing uncompressed data have been presented. In these data structures the data is completely memory resident and instantly accessible. Thus a new issue comes up with the use of compression: Memory for concurrently storing the compressed and uncompressed data is required. The memory requirements of the compressed data is proportional

Figure 4.20: This figure shows the affected case (dark color) after a neighbor (light color) has changed its address. Only the affected fields are updated for each case. The following list is stored for neighbor 4 (yellow): (7,4),(7,7),(1,2),(1,4),(1,7),(4,2),(4,4). This list is to be interpreted as follows: For neighbor 4 the following fields have to be updated: entry 4 of case 7, entry 7 of case 7, entry 2 of case 1, etc.

with the size of the data-set, whereas the memory requirements for the uncompressed data depends on the way of processing the data. For example, processing the data slice by slice would require only a memory area of the size of a slice for processing. The slices to be processed would be decompressed successively into this memory area. The handling of the compressed data and its decompression is discussed in the following chapter.

#### Compression and Memory Usage

For the compression of the data blocks, a LZ77 descendent compression algorithm is used. It is the so-called LZO [11], the Lempel-Ziv-Oberhumer compression algorithm, which was developed by Markus Oberhumer in 1994.

Figure 4.21: Relative addressing scheme at the border in the shared block layout.

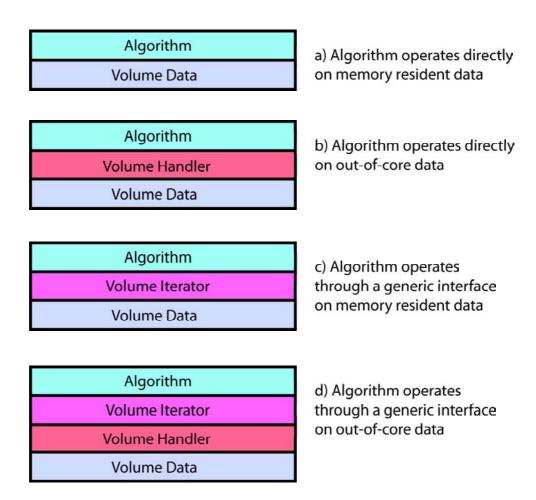

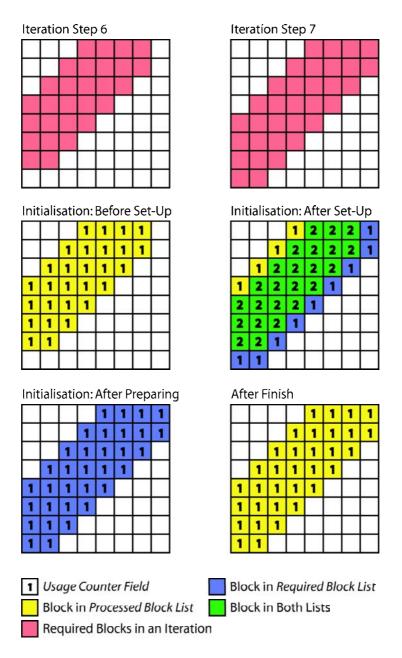

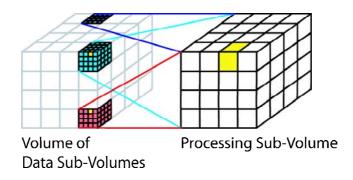

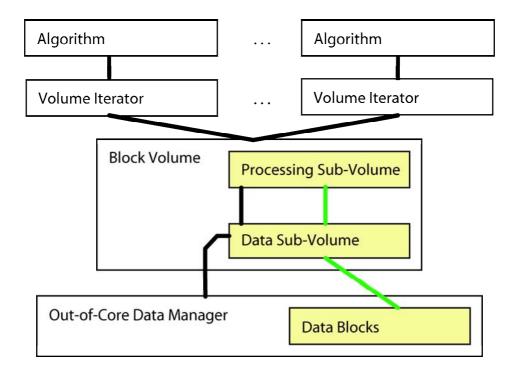

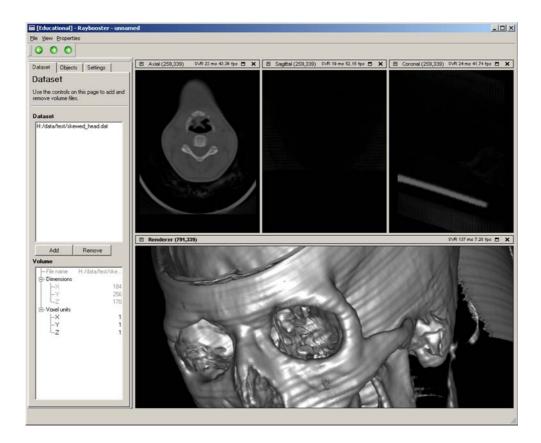

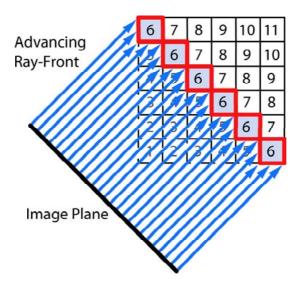

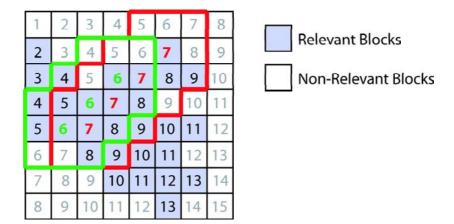

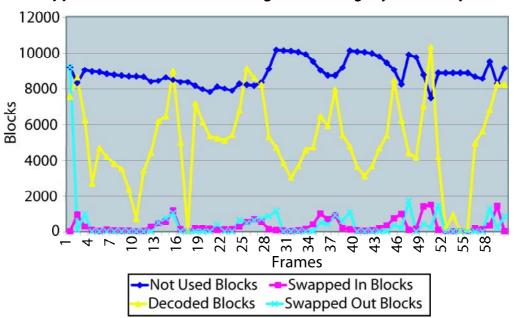

It seems not to be very well known, but is used occasionally in the Linux community. The compression and decompression is slightly faster, than of other LZ77 variants, but is not required to compress better, because speed is the more important issue.